近日,RISC-V指令集和开源硬件的领导者SiFive宣布,公司完成了6540万美元(约合人民币4.5亿)的融资。其中,移动芯片市场的巨头高通也参与了SiFive的融资。

2019年2月,西部数据公司在德国纽伦堡嵌入式世界展上介绍了其产品已经使用了RISC-V架构处理器,每年出货超过10亿颗RISC-V芯片,未来还将翻倍。RISC-V基金会被邀请在纽伦堡大会上举办一个全天的课程和RISC-V专区展示,包括Andes Technology、CloudBEAR、GreenWaves Technologies、Imperas Software、SiFive、Syntacore和UltraSoC等成员公司和大学的演讲。展览期间笔者看到许多著名的嵌入式软件和工具公司,都开始支持RISC-V。比如,德国SEGGER、劳特巴赫、瑞典IAR、Amazon FreeRTOS、嵌入式芯片公司NXP和Microchip,都展示出他们的RISC-V MCU产品。

RISC-V是开源指令集架构

RISC-V是一种开源的指令集架构,它不是一款CPU产品。一个CPU支持的指令和指令的字节级编码,就是CPU的指令集(ISA)。ISA在CPU软件和CPU硬件设计者之间,提供了一个抽象层(接口)。

不同的CPU家族,例如Intel X86、IBM/Freescale PowerPC和ARM,都有不同的ISA。RISC-V是其中唯一的开源ISA,它起源于加州伯克利大学,采用开源BSD license,任何企业、大学和个人都可以遵循RISC-V架构设计CPU,现在全球已有几十个开源版本RISC-V CPU核。

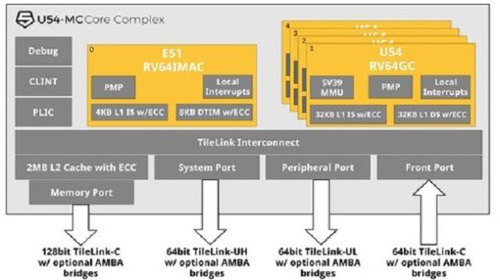

商业公司定制适合自己使用的RISC-V内核,比如西部数据的SweRV(RISCV 32IMC Core),还有一些商业IP公司开发RISC-V CPU IP,比如名气最多的SiFive已经有E和S核2、3、5、7四大系列,覆盖32位―64位嵌入式和高端应用处理器领域。

如何管理RISC-V开源项目?RISC-V基金会成立于2015年,由超过235名成员组成,其中有20家中国机构。它是开放、协作的软件和硬件创新者社区,基金会指导未来发展并推动RISC-V ISA广泛应用。

中国有RISC-V产业和中国开放指令生态(RISC-V)两个联盟,推动RISC-V在中国的发展。

RISC-V具有三大优势

RISC-V最大的优势就是开源和免费。免费意味着RISC-V可以帮助开发者低成本完成CPU设计,如果最终量产,那么就免去面对版税纠纷。ISA开源意味着开发者可以针对特定应用场景,比如近期火热的AIoT市场,创造自己的AIoT芯片架构。当然,基金会鼓励使用RISC-V指令集标准模块或者组合。比如,苏黎世联邦理工大学(ETH Zurich)开源的Zero-riscy内核,采用是RV32IMC,RV32I指令加上M扩展和C扩展,M指的整数乘法和除法,C指的是压缩。NXP织女星开发板(VGEA)MCU采用的就是Zero―riscy开源内核。

RISC-V第二个优势就是简单。基础指令集只有40多条,短小精悍的架构和模块化指令集让使用RISC-V技术的芯片设计者,可以开发出很简单的RISC-V CPU。该CPU功耗可以很小,代码密度也比较低。为了满足嵌入式和物联网对代码体积的高要求,RISC-V定义了一种可选的压缩(Compressed)指令子集,由字母C表示,也可以由RVC表示。测试表明,RV32C的代码体积相比RV32的代码体积减少了40%,与ARM、MIPS和x86等架构相比,都有不错的表现,甚至与ARM Thumb-2基本一样。

RISC-V第三个优势是灵活性。RISC-V架构通过预留大量的编码空间和4条用户指令,可以帮助用户扩展指令集。这个特性在现在的AIoT和信息安全市场,获得了特别的关注。

RISC-V商业IP公司,比如,Andes(晶心科技),还提供了定制化指令工具Andes Custom Extension,让用户在做应用加速的时候,可以达到更快、更有效率的方式。

多核异构是RISC-V架构芯片设计的一个特点,比如,法国GreenWave开发的Gap8 CPU,内置8个RISC-V内核和AI加速器,功耗优化的很低,面向AI边缘技术节点设备。

生态建设是关键

决定一款CPU是否能够广泛普及的因素中,架构和指令集并不是最重要的事情。历史上X86横扫桌面电脑、POWERPC独占通讯设备、ARM称雄移动终端,以及8051/PIC/MSP430/ATMEL百花齐放单片机世界,重要的是CPU所拥有的生态环境。比如,一款通用的嵌入式CPU,需要让开发者很方便地接触到中文资料文档、简单易用的开源商业开发工具、固件库、软件库、嵌入式OS和Linux以及丰富设计方案。

生态建设最漫长的环节是大学计划。大学计划做的好,学生从毕业开始,就已经掌握CPU的架构和使用方法。比如,高校的微机原理课程长期以X86和ARM为基础,嵌入式课程多是ARM架构,单片机课程除了ARM还有一些8051。

今天开源的RISC-V架构在高校很受欢迎。在嵌入式系统联谊会组织的“RISC-V架构嵌入式开发研究与实践技术沙龙”上,清华大学陈渝副教授指出,RISC-V来源于学校,已经经过长期探索。而且,它是开源的,学生可以接触到关于它的所有信息,不像x86和Arm,很难深入了解更多细节。所以,RISC-V更容易开发应用软件和操作系统。很多教师选择RUST语言指导学生在RISC-V架构上写一个小操作系统,高校关注RISC-V的老师们越多,或者开设的基于RISC-V课越多,将来毕业学生上手就越快。RISC-V中文图书并不多,芯来科技创始人胡振波的两本书是学习RISC-V的宝典。最近开始的由NXP发起的Open-ISA开源社区RISC-V MCU创新大赛也是RISC-V生态建设的很好的尝试,希望能在更多的电子、嵌入式和物联网大赛中看到RISC-V芯片的身影。

标准化还是多样化?

现有的CPU架构多是通用性的。在IoT场景中,许多智能分析工作正在向边缘转移。根据特定的需求,使用RISC-V架构定制化IoT芯片更灵活,而且有针对性。现在RISC-V架构的设计,除了基础的指令集保证系统软件、开发环境的兼容性之外,它本身允许按照新的不同开发应用进行扩展,这样可以保证IoT应用中的专用性需求。

NXP中国MCU高级经理梁平最近撰文指出:“对于这种非标准的部分,将较难受益于丰富的生态机制,其生产厂家自行提供相应的支持和配套的解决方案,例如需要修改编译器以支持新的指令、需要增改配置调试工具以适应新的总线或存储接口等。”

笔者观察到,著名的嵌入式编译器公司最近发布的IAR Embedded Workbench for RISC-V也只能支持RV32IM/IMC/IMF/IMFC/IMFD/IMFDC基础指令和标准扩展指令集。各种定制化的芯片只能支持该芯片企业自己维护的工具链,每家芯片公司维护自身RISC-V架构的编译器、SDK、工具链,基于GCC、LLVM等实现开源化,是一个耗时耗力巨大的工程。期待未来RISC-V与Linux基金会的合作,带来RISC-V软件的突破。然而,要使RISC-V真正在商业基础上起飞,还需要商业级工具和软件。

物联网和嵌入式将是RISC-V最先落地和最大的应用市场。因为生态的关系,相当一段时间内,RISC-V将与ARM同行发展,即一个设计中,既能使用ARM也能使用RISC-V,或者同一颗芯片里,可以同时有两种内核。RISC-V发展中要防范碎片化,联盟应加强引导,先是做标准化,共同做大RISC-V蛋糕,然后才是差异化。未来RISC-V生态环境要从围绕芯片设计转向开发者教育和实践阶段。据悉今年夏末,国内某著名MCU企业将推出RISC-V通用MCU,届时RISC-V“谈芯”将转向“用芯”,智联网时代的嵌入式开发者将更方便的评估和使用RISC-V这一新技术。

作者何小庆,系中国软件行业协会嵌入式系统分会副理事长

http:www.cps800.com/news/61952.htm