DDS(DiFeet Digital Frequency Synthesis)即直接数字式频率合成,是从相位概念出发直接合成所需波形的一种频率合成技术。与传统信号源所采用的用模拟方式生成信号不同,它是将先进的数字信号处理理论与方法引入信号合成领域。DDS技术在精确度、灵活度等方面都超过模拟信号发生器。并且DDS可实现相位连续变化,且具有良好频谱的信号,这是传统方法无法实现的。

FPGA的迅速发展为DDS提供了更加优良的技术手段,它具有处理速度快、可靠性高等特点。SOPC(System On Programmable Chip,片上可编程系统)是一种灵活、高效的SOC解决方案。它以IP Core为基础,将处理器、存储器、IO口等系统设计需要的功能模块集成到一个FPGA器件上,构建成一个可编程的片上系统,具有灵活的设计方式。本设计综合以上软硬件可编程协同设计技术,使得DDS电路在灵活性,可行性,精确性等方面得到很大提高。

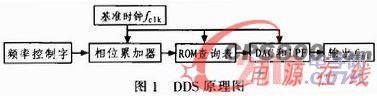

1 DDS的基本原理

DDS信号发生器是由:频率控制字、相位累加器、ROM表、D/A转换器以及模拟低通滤波器LPF组成,原理框图如图1所示。

首先对波形的一个周期进行连续采样,通过计算得到每一点对应的幅度值,然后以二进制格式存放在数据文件中。在时钟脉冲fclk驱动下,每个时钟周期内频率控制字与相位累加器累加一次,产生ROM查找表的地址值,随后通过查表变换,地址值被转化为信号波形的数字幅度序列,即可得到幅度上离散的波形,再由数模变换器(D/A)将表示波形幅度的数字序列转化为模拟量。最后经由LPF将D/A输出的阶梯状波形平滑为所需的连续波形。理论上,采样点数越多,生成波形精确度越高。

2 基于FPGA的DDS设计

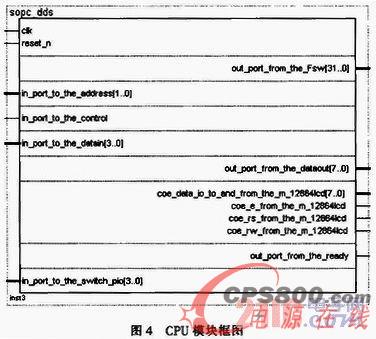

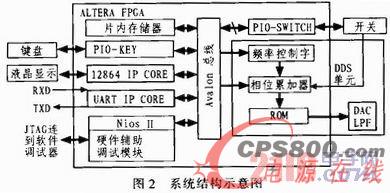

本设计在Altera的EP2C35F672C8芯片的基础上,在SOPCBuilder和OuartusⅡ开发环境下,利用SOPC技术,在FPGA中集成Altera的嵌入式软核处理器NiosⅡ和其他外设,将硬件系统与软件集成在单一可编程芯片中,从而实现片上的系统级设计。系统框图如图2所示,由DDS基本单元(由频率控制字,相位累加器,ROM,DAC,LPF构成),FPGA外部硬件资源(拨扭开关SWTCH、键盘KEY、LCD12864)和NiosⅡ处理器系统等构成了基本电路。四位拨扭开关选择输出波形,键盘控制输出波形信号频率,LCD12864显示波形信号参数,各硬件模块之间的协调工作通过NiosⅡ微处理器在图形化开发环境NiosⅡIDE下用C语言来编程实现控制。

3 各模块设计

3.1 波形数据存储方式

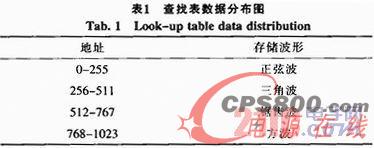

通过对DDS基本原理的分析得知只需更换波形存储器中的波形采样数据,就可以得到所需波形的信号。波形数据存储方式包括顺序存储方式和间隔存储方式,本设计采用顺序存储方式将方波,三角波,正弦波,锯齿波4种波形采样数据全部依次存储在一个查找表里,数据分布情况如表1所示。通过改变寻址首地址,并在该波形数据存储地址范围内循环寻址,从而实现对所需信号波形的输出。具体实现方法在累加控制模块中有介绍。

DDS模块中的波形数据存储器是用QuartusⅡ中的MegaWizard Plug_In Manager工具添加的LPM_ROM IP核,此存储器ROM是用波形存储文件.mif进行初始化,波形数据可以用matlab等工具生成,用matlab生成4种波形的波表数据程序如下:

- 1

- 2

- 3

- 总3页

来源:互联网

http:www.cps800.com/news/33490.htm